Pixel Visual Core - Pixel Visual Core

Pixel Visual jádro ( PVC ) je série ARM založené na systému balení (SIP) obrazových procesorů navržený Google . PVC je plně programovatelný obraz , vize a AI vícejádrová architektura specifická pro doménu (DSA) pro mobilní zařízení a v budoucnu pro IoT . Poprvé se objevil v Google Pixel 2 a 2 XL, které byly představeny 19. října 2017. Také se objevil v Google Pixel 3 a 3 XL . Počínaje Pixel 4 byl tento čip nahrazen Pixel Neural Core .

Dějiny

Google již používá Qualcomm Snapdragon s CPU , GPU , IPJ a DSP zvládnout jeho zpracování obrazu pro své Google Nexus a Google Pixel zařízení. S rostoucím významem technik výpočetní fotografie vyvinul Google Pixel Visual Core (PVC). Google tvrdí, že PVC používá méně energie než použití CPU a GPU, zatímco je stále plně programovatelný, na rozdíl od jejich integrovaného obvodu specifického pro aplikaci tenzorů (TPU) (ASIC). Klasická mobilní zařízení skutečně vybavují procesor obrazového signálu (ISP), který je potrubím pro zpracování obrazu s pevnou funkcí . Na rozdíl od toho má PVC flexibilní programovatelnou funkčnost, která se neomezuje pouze na zpracování obrazu.

PVC v Google Pixel 2 a 2 XL je označen SR3HX X726C502.

PVC v Google Pixel 3 a 3 XL je označen SR3HX X739F030.

Díky PVC získaly Pixel 2 a Pixel 3 mobilní DxOMark 98 a 101. Posledním z nich bylo nejlépe hodnocené jednooké objektivové skóre DxOMark spojené s iPhone XR.

Software Pixel Visual Core

Typický program zpracování obrazu z PVC je napsán v Halide . V současné době podporuje pouze podmnožinu programovacího jazyka Halide bez operací s plovoucí desetinnou čárkou a s omezenými vzory přístupu k paměti. Halide je jazyk specifický pro doménu, který umožňuje uživateli oddělit algoritmus a plánování jeho provádění. Tímto způsobem může vývojář napsat program, který je optimalizován pro architekturu cílového hardwaru.

Pixel Visual Core ISA

PVC má dva typy architektury instrukční sady (ISA) , virtuální a fyzickou. Nejprve je jazykový program na vysoké úrovni zkompilován do virtuálního ISA (vISA) , inspirovaného RISC-V ISA, který zcela abstrahuje od generování cílového hardwaru. Poté je program vISA zkompilován do tzv. Fyzického ISA (pISA) , což je VLIW ISA. Tento krok kompilace bere v úvahu cílové hardwarové parametry (např. Pole velikosti PE, velikost STP atd.) A specifikuje výslovně pohyby paměti. Oddělení vISA a pISA umožňuje, aby první byla nezávislá na architektuře a generaci, zatímco pISA lze kompilovat offline nebo prostřednictvím kompilace JIT .

Architektura Pixel Visual Core

Pixel Visual Core je navržen tak, aby byl škálovatelnou vícejádrovou energeticky účinnou architekturou v rozmezí od sudých čísel mezi 2 až 16 jádrovými vzory. Jádrem PVC je jednotka zpracování obrazu (IPU), programovatelná jednotka přizpůsobená pro zpracování obrazu. Architektura Pixel Visual Core byla také navržena buď jako vlastní čip, jako SR3HX, nebo jako blok IP pro systém na čipu (SOC) .

Jednotka zpracování obrazu (IPU)

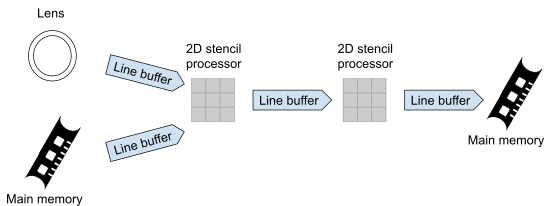

Jádro IPU má procesor šablony (STP), fond vyrovnávacích pamětí linky (LBP) a NoC . STP poskytuje hlavně 2-D SIMD pole procesorových prvků (PE) schopných provádět výpočty vzorníků , malé sousedství pixelů. Ačkoli se to zdá podobné výpočtům systolického pole a vlnoplochy, STP má explicitní softwarově řízený pohyb dat. Každý PE má 2 × 16bitové aritmetické logické jednotky (ALU) , 1 × 16bitovou jednotku multiplikátoru a akumulátoru (MAC) , 10x 16bitové registry a 10x 1bitový predikátový registr.

Pool Line Buffer (LBP)

Vzhledem k tomu, že jednou z energeticky nejnákladnějších operací je přístup na DRAM, má každý STP dočasné vyrovnávací paměti ke zvýšení datové lokality , konkrétně LBP. Použitý LBP je 2-D FIFO, který umožňuje různé velikosti čtení a zápisu. LBP používá model chování více spotřebitelů s jedním výrobcem. Každý LBP může mít osm logických LB pamětí a jednu pro operace vstupu a výstupu DMA . Vzhledem ke skutečně vysoké složitosti paměťového systému návrháři PVC uvádějí řadič LBP jako jednu z nejnáročnějších součástí. Použitý NoC je kruhová síť na čipu, která slouží ke komunikaci s pouze sousedními jádry pro úsporu energie a zachování zpracovaného výpočetního vzoru.

Procesor šablony (STP)

STP má 2-D pole PE: například 16x16 pole plných PE a čtyři pruhy zjednodušených PE zvaných „halo“ . STP má skalární procesor, zvaný skalární dráha (SCL), který přidává řídicí instrukce s malou pamětí instrukcí. Poslední složkou STP je jednotka pro ukládání zátěží nazývaná generátor listů (SHG), kde je listem jednotka přístupu do paměti PVC.

Souhrn designu SR3HX

SR3HX PVC je vybaven 64bitovým procesorem ARMv8a ARM Cortex-A53 , 8x jádry jednotky pro zpracování obrazu (IPU), 512 MB LPDDR4 , MIPI, PCIe. Každá jádra IPU mají 512 aritmetických logických jednotek (ALU) skládajících se z 256 procesorových prvků (PE) uspořádaných jako dvourozměrné pole 16 x 16. Tato jádra provádějí vlastní VLIW ISA. Existují dva 16bitové ALU na zpracovatelský prvek a mohou pracovat třemi různými způsoby: nezávislé, spojené a fúzované. SR3HX PVC se vyrábí jako SiP společností TSMC pomocí jejich procesu 28HPM HKMG . Byl navržen na více než 4 roky ve spolupráci se společností Intel . (Codename: Monette Hill) Google tvrdí, že SR3HX PVC je 7-16x energeticky účinnější než Snapdragon 835 . A že SR3HX PVC může provádět 3 biliony operací za sekundu, HDR + může běžet 5x rychleji a za méně než desetinu energie než Snapdragon 835 . Podporuje Halide pro zpracování obrazu a TensorFlow pro strojové učení. Aktuální čip běží na 426 MHz a jediná IPU je schopna provádět více než 1 TeraOPS.

Reference

- ^ a b c Cutress, Iane. „Hot Chips 2018: Blog Google Pixel Visual Core Live (10:00 PT, 17:00 UTC)“ . www.anandtech.com . Citováno 2019-02-02 .

- ^ a b c d e f g h i j Hennessy, John; Patterson, David (2017). Počítačová architektura: kvantitativní přístup (šesté vydání). Morgan Kaufmann. 579–606. ISBN 978-0-12-811905-1 .

- ^ „Google Pixel 2 XL Teardown“ . iFixit . 19. 10. 2017 . Citováno 2019-02-02 .

- ^ „Google Pixel 3 XL Teardown“ . iFixit . 16. 10. 2018 . Citováno 2019-02-02 .

- ^ „Pixel 2 DxOMark“ .

- ^ „Pixel 3 DxOMark“ .

- ^ „iPhone XR DxOMark“ .

- ^ a b c d „Pixel Visual Core: Plně programovatelný obrazový, vizuální a AI procesor společnosti Google pro mobilní zařízení. HotChips2018“ (PDF) .

- ^ „Pixel Visual Core (PVC) - Google - WikiChip“ . en.wikichip.org . Citováno 2019-02-02 .

- ^ „Google uzavřel partnerství s Intelem pro čip Pixel Visual Core v Pixel 2“ . xda-vývojáři . 25. 10. 2017 . Citováno 2019-02-02 .

- ^ a b „Pixel Visual Core: zpracování obrazu a strojové učení na Pixel 2“ . Google . 17. 10. 2017 . Citováno 2019-02-02 .