Jednotka s plovoucí desetinnou čárkou - Floating-point unit

Jednotka s plovoucí desetinnou čárkou ( FPU , hovorově matematický koprocesor ) je část počítačového systému speciálně navrženého k provádění operací s čísly s plovoucí desetinnou čárkou . Typickými operacemi jsou sčítání , odčítání , násobení , dělení a druhá odmocnina . Některé FPU mohou také provádět různé transcendentální funkce, jako jsou exponenciální nebo trigonometrické výpočty, ale přesnost může být velmi nízká, takže některé systémy dávají přednost výpočtu těchto funkcí v softwaru.

V obecných počítačových architekturách může být jedna nebo více FPU integrováno jako prováděcí jednotky v centrální procesorové jednotce ; mnoho vestavěných procesorů však nemá hardwarovou podporu pro operace s plovoucí desetinnou čárkou (i když je stále více mají jako standardní, alespoň 32bitové).

Když CPU spouští program, který vyžaduje operaci s plovoucí desetinnou čárkou, existují tři způsoby, jak ji provést:

- Emulátor jednotky s plovoucí desetinnou čárkou (knihovna s plovoucí desetinnou čárkou).

- Doplňkový FPU.

- Integrovaná FPU.

Dějiny

V roce 1954 měl IBM 704 aritmetiku s plovoucí desetinnou čárkou jako standardní funkci, jedno z hlavních vylepšení oproti svému předchůdci IBM 701 . To bylo přeneseno na jeho nástupce 709, 7090 a 7094.

V roce 1963 společnost Digital oznámila PDP-6 , který měl jako standardní funkci plovoucí čárku.

V roce 1963 GE-235 představoval „pomocnou aritmetickou jednotku“ pro výpočty s plovoucí desetinnou čárkou a dvojitou přesností.

Historicky některé systémy implementovaly pohyblivou řádovou čárku s koprocesorem, nikoli jako integrovanou jednotku (ale nyní kromě CPU, např. GPU - což jsou koprocesory, které nejsou vždy integrovány do CPU - mají zpravidla FPU, zatímco první generace GPU nikoli 't). Může to být jeden integrovaný obvod , celá deska s obvody nebo skříň. Tam, kde nebyl poskytnut hardware pro výpočet s pohyblivou řádovou čárkou, se výpočty s pohyblivou řádovou čárkou provádějí v softwaru, který zabere více času procesoru, ale vyhne se nákladům na další hardware. Pro konkrétní počítačovou architekturu mohou být instrukce jednotky s plovoucí desetinnou čárkou emulovány knihovnou softwarových funkcí; to může umožnit spuštění stejného objektového kódu na systémech s hardwarem s plovoucí desetinnou čárkou nebo bez něj. Emulaci lze implementovat na libovolné z několika úrovní: v CPU jako mikrokód (není to běžná praxe), jako funkce operačního systému nebo v kódu uživatelského prostoru . Pokud je k dispozici pouze celočíselná funkce, nejčastěji se používají metody emulace CORDIC s pohyblivou řádovou čárkou.

Ve většině moderních počítačových architektur existuje určité dělení operací s plovoucí desetinnou čárkou z celých operací. Toto rozdělení se výrazně liší podle architektury; některé mají vyhrazené registry s plovoucí desetinnou čárkou, zatímco některé, jako Intel x86 , to berou tak daleko, jako nezávislá schémata taktování .

Rutiny CORDIC byly implementovány v koprocesorech Intel x87 ( 8087 , 80287, 80387) až do řady mikroprocesorů 80486 , stejně jako v Motorola 68881 a 68882 pro některé druhy instrukcí s plovoucí desetinnou čárkou, hlavně jako způsob, jak snížit počet bran (a složitost) subsystému FPU.

Operace s pohyblivou řádovou čárkou jsou často propojeny . V dřívějších superskalárních architekturách bez obecného provádění mimo pořadí byly operace s plovoucí desetinnou čárkou někdy propojeny odděleně od celočíselných operací.

Modulární architektura mikroarchitektury Bulldozer využívá speciální FPU s názvem FlexFPU, který využívá simultánní multithreading . Každé fyzické celočíselné jádro, dvě na modul, má jedno vlákno , na rozdíl od Hyperthreadingu společnosti Intel , kde dvě virtuální souběžná vlákna sdílejí prostředky jednoho fyzického jádra.

Knihovna s pohyblivou řádovou čárkou

Některý hardware s plovoucí desetinnou čárkou podporuje pouze nejjednodušší operace: sčítání, odčítání a násobení. Ale i ten nejsložitější hardware s plovoucí desetinnou čárkou má omezený počet operací, které může podporovat-například žádné FPU přímo nepodporují aritmetiku libovolné přesnosti .

Když CPU spouští program, který vyžaduje operaci s plovoucí desetinnou čárkou, která není přímo podporována hardwarem, procesor používá řadu jednodušších operací s plovoucí desetinnou čárkou. V systémech bez hardwaru s pohyblivou řádovou čárkou jej CPU emuluje pomocí řady jednodušších aritmetických operací s pevným bodem, které běží na celočíselné aritmetické logické jednotce .

Software, který uvádí nezbytné řady operací k emulaci operací s plovoucí desetinnou čárkou, je často zabalen v knihovně s plovoucí desetinnou čárkou .

Integrované FPU

V některých případech mohou být FPU specializované a děleny mezi jednodušší operace s pohyblivou řádovou čárkou (hlavně sčítání a násobení) a složitější operace, jako je dělení. V některých případech mohou být v hardwaru nebo mikrokódu implementovány pouze jednoduché operace , zatímco složitější operace jsou implementovány jako software.

V některých současných architekturách je funkce FPU kombinována s jednotkami SIMD pro provádění výpočtu SIMD; příkladem toho je rozšíření sady instrukcí x87 o sadu instrukcí SSE v architektuře x86-64 používané v novějších procesorech Intel a AMD.

Doplňkové FPU

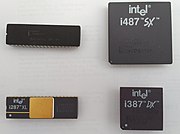

V 80. letech 20. století bylo v mikropočítačích kompatibilních s IBM PC běžné, že FPU byl zcela oddělen od CPU a obvykle se prodával jako volitelný doplněk. Bylo by zakoupeno pouze v případě potřeby pro zrychlení nebo povolení programů náročných na matematiku.

IBM PC, XT a většina kompatibilních na základě 8088 nebo 8086 měla zásuvku pro volitelný koprocesor 8087. AT a 80286 založené systémy byly obecně soketne pro 80287 a 80386 / 80386SX založené stroje - pro 80387 a 80387SX pořadí, i když ty brzy byly soketne na 80287, protože 80387 ještě neexistoval. Jiné společnosti vyráběly koprocesory pro řadu Intel x86. Patřily mezi ně Cyrix a Weitek .

Pro rodinu Motorola 68000 , 68881 a 68882 byly k dispozici koprocesory . Ty byly běžné v Motorola 68020 / 68030 založené pracovní stanice , jako je Sun-3 série. Byly také běžně přidávány do modelů vyšší řady Apple Macintosh a Commodore Amiga , ale na rozdíl od systémů kompatibilních s IBM PC nebyly zásuvky pro přidání koprocesoru v systémech nižší třídy tak běžné.

Existují také přídavné koprocesorové jednotky FPU pro mikrokontrolérové jednotky (MCU/ μC)/ jednodeskový počítač (SBC), které slouží k poskytování aritmetických schopností s pohyblivou řádovou čárkou . Tyto přídavné FPU jsou nezávislé na hostitelském procesoru, mají své vlastní programovací požadavky ( operace , sady instrukcí atd.) A často jsou vybaveny vlastním integrovaným vývojovým prostředím (IDE).

Viz také

- Aritmetická logická jednotka (ALU)

- Jednotka generování adres (AGU)

- Načíst - uložit jednotku

- CORDIC rutiny se používají v mnoha FPU k implementaci funkcí, ale nijak výrazně nezvyšují počet bran

- Popravčí jednotka

- Standard IEEE 754 s plovoucí desetinnou čárkou

- Šestnáctková IBM s plovoucí desetinnou čárkou

- Jednotka pro zpracování grafiky

- Operace násobení - akumulace

Reference

Další čtení

- Filiatreault, Raymond (2003). „JEDNODUCHO FPU“ .